As data centers consume ever more electricity, UC San Diego engineers have built a prototype chip that converts power far more efficiently using a hybrid piezoelectric design. The work could pave the way for smaller, cooler and more sustainable computing hardware.

Data centers that power cloud computing, AI and streaming services are devouring electricity at a growing pace. A new chip design from University of California San Diego engineers aims to make that power use much more efficient.

The team has built a prototype chip that performs one of the most basic but critical jobs in electronics: turning high voltages from a power source into the much lower voltages that processors and memory actually use. In lab tests, the chip handled the kind of voltage conversion used in modern data centers with very high efficiency, pointing to a possible path toward smaller, cooler and more sustainable computing systems.

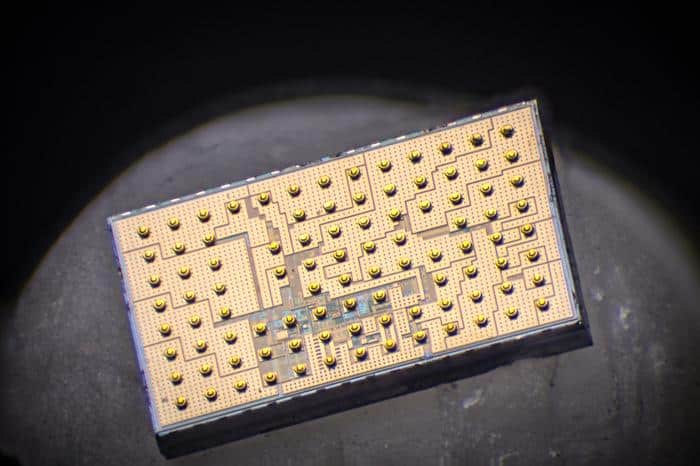

Caption: A chip designed to convert high voltages into lower levels in electronics — a process known as DC-DC step-down conversion — more efficiently using a piezoelectric resonator.

Credit: David Baillot/UC San Diego Jacobs School of Engineering

The work, published in Nature Communications, focuses on a circuit block called a DC-DC step-down converter. This component sits between a power supply and sensitive electronics, acting like a smart valve that reduces voltage to exactly the level a chip needs.

In many data centers, power is distributed at about 48 volts to reduce losses as electricity travels across racks of servers. But the graphics processing units, or GPUs, that run AI models and graphics workloads typically operate at just 1 to 5 volts. Bridging that gap efficiently, in very tight spaces on crowded circuit boards, has become a major engineering challenge.

Most of today’s step-down converters rely on magnetic components called inductors. These have been optimized for decades, but they are now running into physical limits, especially when asked to handle large differences between input and output voltage without wasting energy or taking up too much space.

“We’ve gotten so good at designing inductive converters that there’s not really much room left to improve them to meet future needs,” senior author Patrick Mercier, a professor in the Department of Electrical and Computer Engineering at the UC San Diego Jacobs School of Engineering, said in a news release.

To break through those limits, Mercier and his team, including first author and doctoral student Jae-Young Ko, turned to a different kind of device: piezoelectric resonators. These tiny components store and move energy through mechanical vibrations rather than magnetic fields. In principle, they can be made very small, pack a lot of power into a compact footprint and be easier to manufacture at scale.

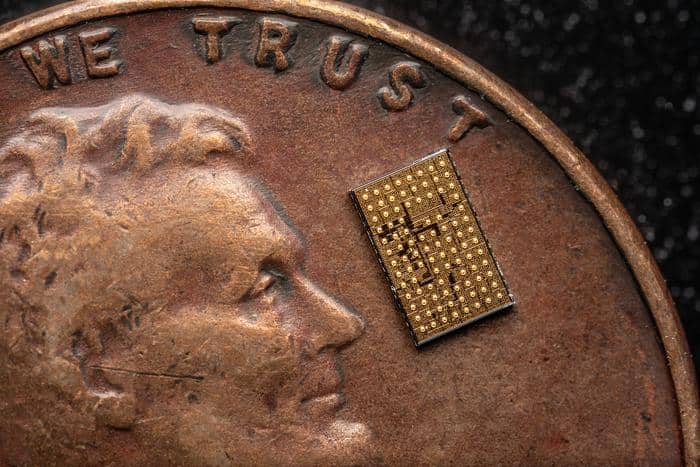

Caption: The new DC-DC step-down conversion chip shown on a U.S. penny for scale.

Credit: David Baillot/UC San Diego Jacobs School of Engineering

Mercier added that compared with traditional inductive converters, piezoelectric-based designs “have a lot of room to grow and have the potential to deliver better performance than anything that’s come before them.”

Early versions of piezoelectric converters, however, have struggled when asked to handle large voltage drops, such as from 48 volts down to a few volts. They often lose efficiency and cannot deliver enough current to feed power-hungry processors.

The UC San Diego team’s key advance is a hybrid circuit that combines a piezoelectric resonator with a network of small, commercially available capacitors arranged in a carefully engineered way. This architecture creates multiple paths for power to flow, reduces wasted energy and lightens the load on the vibrating resonator.

The researchers implemented this design in a prototype chip and tested it on a demanding task: converting 48 volts down to 4.8 volts, a level commonly used in data center hardware. The chip reached a peak efficiency of 96.2% and delivered about four times more output current than earlier piezoelectric-based converters, according to the team.

Those numbers suggest that hybrid piezoelectric converters could one day rival or surpass the performance of today’s best magnetic-based converters, while potentially shrinking the size of power management circuits on boards packed with GPUs and other processors.

Better power conversion is not just an engineering nicety. As AI models grow larger and more complex, data centers are adding racks of GPUs and other accelerators, driving up electricity use and heat output. Improving the efficiency of every step in the power chain, from the grid down to the chip, is one of the most direct ways to curb that growth in energy demand.

The new design is still at the research stage, and there are practical hurdles before it can be deployed in commercial systems. One major challenge is packaging, Mercier explained. Because piezoelectric resonators physically vibrate as they operate, they cannot simply be soldered onto circuit boards using standard techniques without risking damage or performance loss. New integration strategies will be needed to embed them reliably into real-world hardware.

Mercier is clear that the technology is not ready to drop into data centers yet.

“Piezoelectric-based converters aren’t quite ready to replace existing power converter technologies yet,” Mercier said. “But they offer a trajectory for improvement. We need to continue to improve on multiple areas — materials, circuits and packaging — to make this technology ready for data center applications.”

Future work will focus on refining the materials used in the resonators, optimizing the circuit design for even higher power levels and efficiency, and developing packaging methods that protect the vibrating components while allowing them to be integrated into standard electronic systems.

If those efforts succeed, tomorrow’s AI servers and cloud platforms could run on power electronics that waste far less energy, helping data centers keep up with demand without sending electricity use through the roof.